建行官网seo人员的相关薪资

典型电路设计之FIFO设计

FIFO (First In First Out)是一种先进先出的数据缓存器,通常用于接口电路的数据缓存。与普通存储器的区别是没有外部读写地址线,可以使用两个时钟分别进行写和读操作。FIFO只能顺序写入数据和顺序读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

FIFO由存储器块和对数据进出FIFO的通道进行管理的控制器构成,每次只对一个寄存器提供存取操作,而不是对整个寄存器阵列进行。FIFO有两个地址指针,一个用于将数据写入下一个可用的存储单元,一个用于读取下一个未读存储单元的操作。读写数据必须一次进行。

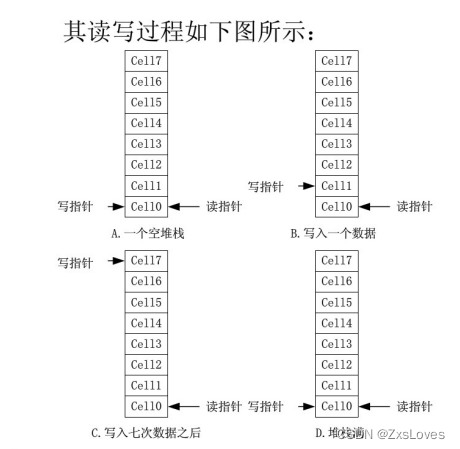

当一个堆栈为空时(图A),读数据指针和写数据指针都指向第一个存储单元,如所示;当写入一个数据时(图B)写数据指针将指向下个存储单元;经过七次写数据操作后(图C)写指针将指向最后一个数据单元;当经过连续八次写操作之后写指针将回到首单元并且显示堆栈状态为满(图D)。数据的读操作和写操作相似,当读出一个数据时,读数据指针将移向下一个存储单元,直到读出全部的数据,此时读指针回到首单元,堆栈状态显示为空。

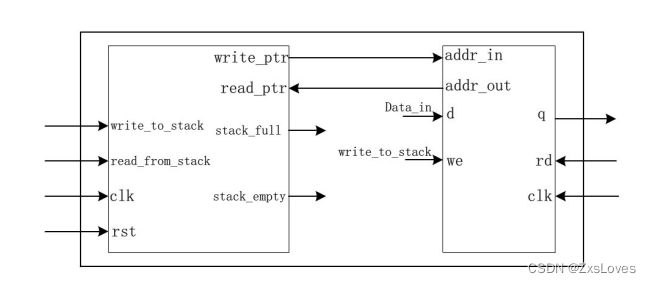

一个FIFO的组成一般包括两个部分:地址控制部分和存储数据的RAM部分。如下图所示。地址控制部分可以根据读写指令生成RAM地址。RAM用于存储堆栈数据,并根据控制部分生成的地址信号进行数据的存储和读取操作。这里的RAM采用的是前面提到的双口RAM。

例用Verilog HDL 设计深度为8,位宽为8的FIFO

下面是verilog代码

module FIFO_buffer(clk,rst,write_to_stack,read_from_stack,Data_in,Data_out);

input clk,rst;

input write_to_stack,read _from_stack;

input [7:0] Data_in;

output [7:0] Data_out;

wire [7:0]Data_out;

wire stack_full,stack_empty;

wire [2:0] addr_in, addr_out;

.write_to_stack(write_to_stack),.write_ptr(addr_in),

.write_to_stack(write_to_stack),.write_ptr(addr_in),.read_ptr(addr_out),.read_from_stack(read_from_stack),.clk(clk),.rst(rst));

ram_dual U2(.q(Data_out),.addr_in(addr_in),.addr_out(addr_out),.d(Data_in),.we(write_to_stack),.rd(read_from_stack),.clk1(clk),.clk2(Clk));

endmodule

module FIFO_control( write_ptr,read_ptr,stack_full, stack_empty,write_to_stack,

read_from_stack, clk, rst);

parameter stack_width=8;

parameter stack_height=8;

parameter stack_ptr_width=3;

output stack_full;

output stack_empty;

output [stack_ptr_width-1:0] read_ptr;

output [stack_ptr_width-1:0] write_ptr;

input write_to_stack;

input read_from_stack;

input clk;

inputrst;

reg[stack_ptr_width-1:0] read ptr;

reg[stack_ptr_width-1:0] write _ptr;

reg[stack _ptr_width:0] ptr_gap;

reg [stack_width-1:0] Data_out;

reg[stack_width-1:0]stack[stack_height-1:0];

always@(posedge clk or posedge rst)begin

if(rst)begin

Data_out<=0;

read_ptr<=0;

write_ptr<=0;

ptr_gap<=0;

end

else if(write_to_stack && (!stack_full) && (!read_from_stack))begin

write_ptr<=write_ptr+1;

ptr_gap<=ptr_gap+1;

end

else if(!write_to_stack && (!stack_empty) && (read_from_stack))begin

read_ptr<=read_ptr+1;

ptr_gap<=ptr_gap-1;

end

else if(write_to _stack && stack_empty &.& read _from_stack)begin

write_ptr<=write_ptr+1;

ptr_gap<=ptr_gap+1;

end

else if(write _to_stack && stack_full && read_from_stack)begin

read _ptr<=read_ptr+1;

ptr_gap<=ptr_gap-1;

end

else if(write_to_stack && read_from_stack

&& (!stack_full)&&(!stack_empty))begin

read_ptr<=read_ptr+1;

write_ptr<=write_ptr+1;

end

end

endmodule

下面是testbench

module FIFO_tb;

reg clk, rst;

reg [7:0]Data_in;

reg write_to_stack, read_from_stack;

wire[7:0] Data_out;

FIFO_buffer U1(.clk(clk),.rst(rst),.write_to_stack(write_to_stack),

.read_from_stack(read_from_stack),.Data_in(Data_in),

.Data_out(Data_out));

initial

begin

clk=0;

rst=1;

Data_in=0;

write_to_stack=1;

read_from_stack=0;

#5 rst=0;

#155 write_to_stack=0;

read_from_stack=1;

end

always #10 clk=~clk;

initial

begin

repeat(7)

#20 Data_in=Data_in+1;

end

endmodule