网站底部代码特效太原seo软件

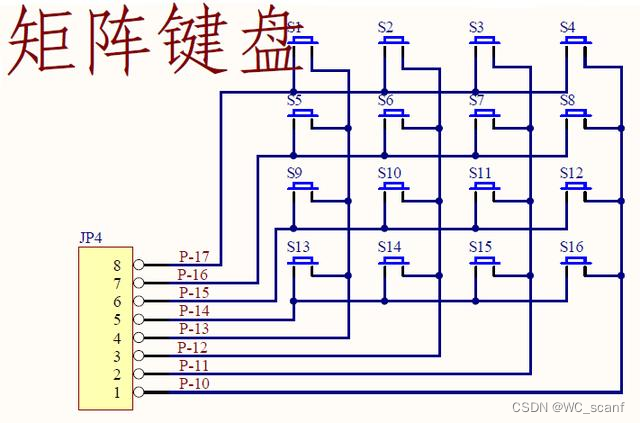

矩阵键盘介绍:

矩阵键盘是使用8个io口来进行16个按键的控制读取,用4条I/O线作为行线,4条I/O线作为列线组成的键盘。在行线和列线的每个交叉点上,设置一个按键。

如图所示:

矩阵键盘扫描的方式有两种: 1.行列扫描,2.逐行/逐列扫描

行列扫描:

将P口的高四位(代表四个行)设置为高电平,将P口的低四位(代表四个列)设置为输入口;行扫描,等待按键被按下,读取P1口的低四位,检查哪一位从低电平变为高电平。列扫描:将P口的高四位(四个行)设置为低电平,将P口的低四位(四个列)设置为高电平。读取P口的低四位,检查哪一位从高电平变为低电平。将两次读取结果组合起来就可以得到当前按键的特征编码。

逐行/逐列扫描:

是给某一行/某一列,高电平,其余七个全部为底电平,这时候读取电平变换,有电平变高表示按键按下,结合给出的行列关系,即可读取按键数据。

实验目的:设计一个可以读取按键按下数据的矩阵键盘

(本实验用的是逐行/逐列扫描方式)

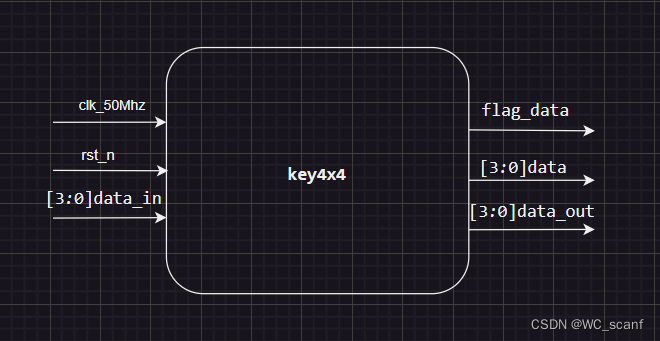

模块框图:

key4x4模块代码

module key4x4

(input wire clk_50Mhz , //系统时钟50Mhzinput wire rst_n , //全局复位input wire [3:0]data_in , //输入逐行扫描信号output reg flag_data , //flag_data为1时表示消抖后检测到按键被按下,维持一个时钟的高电平output reg [3:0]data , //输出按键的特征编码output reg [3:0]data_out //输出逐列扫描信号);//SUM_MAX> SUM_KEY_20MS

parameter SUM_MAX =21'd1_999_999;

parameter SUM_KEY_20MS =22'd999_999; reg [20:0] num;

reg [19:0] num_10ms;reg [1:0] qs;//每隔40ms产生一次内部触发信号

always@( posedge clk_50Mhz or negedge rst_n) begin if (rst_n==1'b0) beginnum <= 22'd0;endelse if (num == SUM_MAX) beginnum <= 22'd0;endelse beginnum <= num +22'd1;end

end //产生逐列扫描信号

always@( posedge clk_50Mhz or negedge rst_n) begin if (rst_n==1'b0) beginqs <=2'd0; end else if(num_10ms == SUM_KEY_20MS) beginqs <= qs ;end else if(num == SUM_MAX) beginqs <= qs +2'd1;end

end //输出逐列扫描信号

always @(posedge clk_50Mhz or negedge rst_n) begin if(rst_n ==1'b0) begindata_out<= 4'b1111;endelse begincase (qs)2'b00:data_out<= 4'b0001; 2'b01:data_out<= 4'b0010; 2'b10:data_out<= 4'b0100; 2'b11:data_out<= 4'b1000; default:data_out<= 4'b1111; endcase end

end//得到当前按键的特征编码

always @(posedge clk_50Mhz or negedge rst_n) begin if(rst_n==1'b0)begindata <=4'b0000;endelse begincase ({data_out,data_in}) 8'b0001_0001 : data <=4'b0000; //08'b0001_0010 : data <=4'b0001; //18'b0001_0100 : data <=4'b0010; //28'b0001_1000 : data <=4'b0011; //38'b0010_0001 : data <=4'b0100; //4 8'b0010_0010 : data <=4'b0101; //58'b0010_0100 : data <=4'b0110; //68'b0010_1000 : data <=4'b0111; //78'b0100_0001 : data <=4'b1000; //88'b0100_0010 : data <=4'b1001; //98'b0100_0100 : data <=4'b1010; //108'b0100_1000 : data <=4'b1011; //118'b1000_0001 : data <=4'b1100; //128'b1000_0010 : data <=4'b1101; //138'b1000_0100 : data <=4'b1110; //148'b1000_1000 : data <=4'b1111; //15default: data <= data; endcase end

end //消抖部分

always@( posedge clk_50Mhz or negedge rst_n) begin if (rst_n==1'b0) beginnum_10ms <=22'd0;end else if (data_in== 4'b0000) beginnum_10ms <=22'd0;end else if ((num_10ms == SUM_KEY_20MS)&&(data_in !=4'b0000)) beginnum_10ms <= num_10ms;endelse beginnum_10ms <= num_10ms+22'd1;end

end//flag_data,产生一个时钟的高电平

always@( posedge clk_50Mhz or negedge rst_n) begin if (rst_n==1'b0) beginflag_data <=1'd0;end else if (num_10ms == SUM_KEY_20MS-1) beginflag_data <=1'd1;endelse beginflag_data <=1'd0; end

end

endmodule