靠谱的建站正规公司品牌策划运营公司

文章目录

- 前言

- 一、CMT(时钟管理单元)

- 1、CMT 简介

- 2、FPGA CMT 框图

- 3、MMCM 框图

- 4、PLL 框图

- 二、创建工程

- 1、创建工程

- 2、PLL IP 核配置

- 3、进行例化

- 三、进行仿真

- 1、创建仿真文件

- 2、进行仿真设置

- 3、进行行为级仿真

- 四、硬件验证

- 1、引脚绑定

- 2、生成比特流文件

- 3、验证

- 五、资源自取

前言

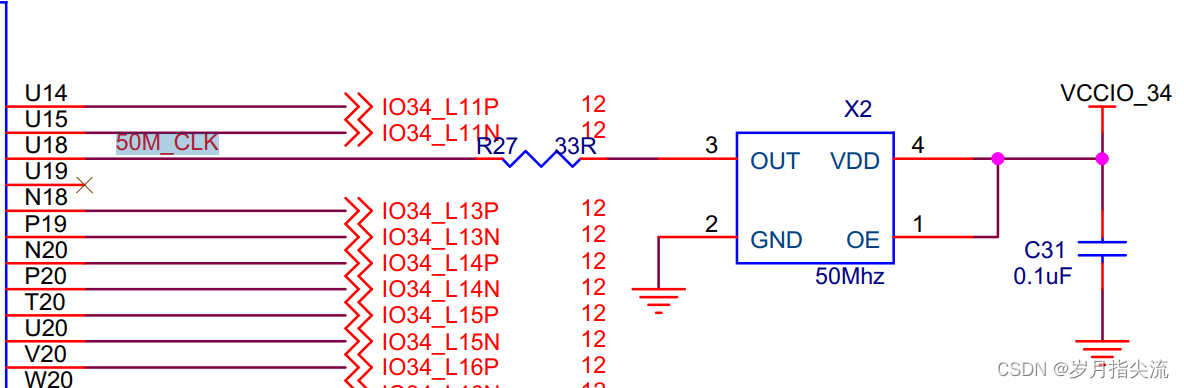

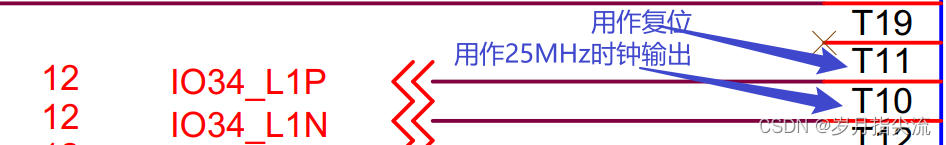

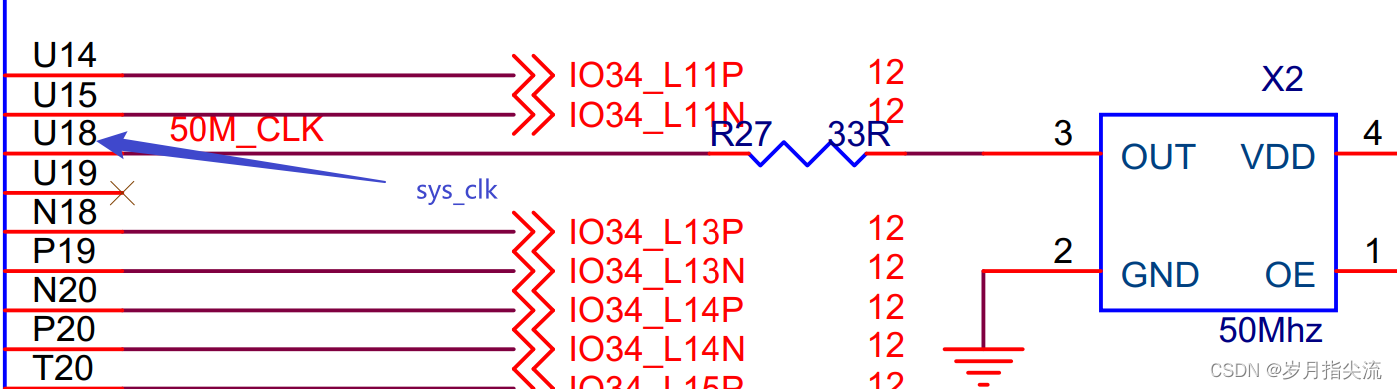

本节介绍一下赛灵思锁相环的一个使用方法,我手头的 AC7020 fpga 开发板上面有一个 50MHz 的晶振连接在 PL 端,晶振输出链接到 FPGA 的全局时钟(MRCC),这个 CLK 可以用来驱动 FPGA 内的用户逻辑电路,该时钟源的原理图如图所示:

但是在我们实际应用当中呢我们可能想要使用特定大小的频率,比如 25MHz 或者 100MHz,那么我们可以使用赛灵思的锁相环的 IP 实现它的时钟分频或者倍频。

一、CMT(时钟管理单元)

1、CMT 简介

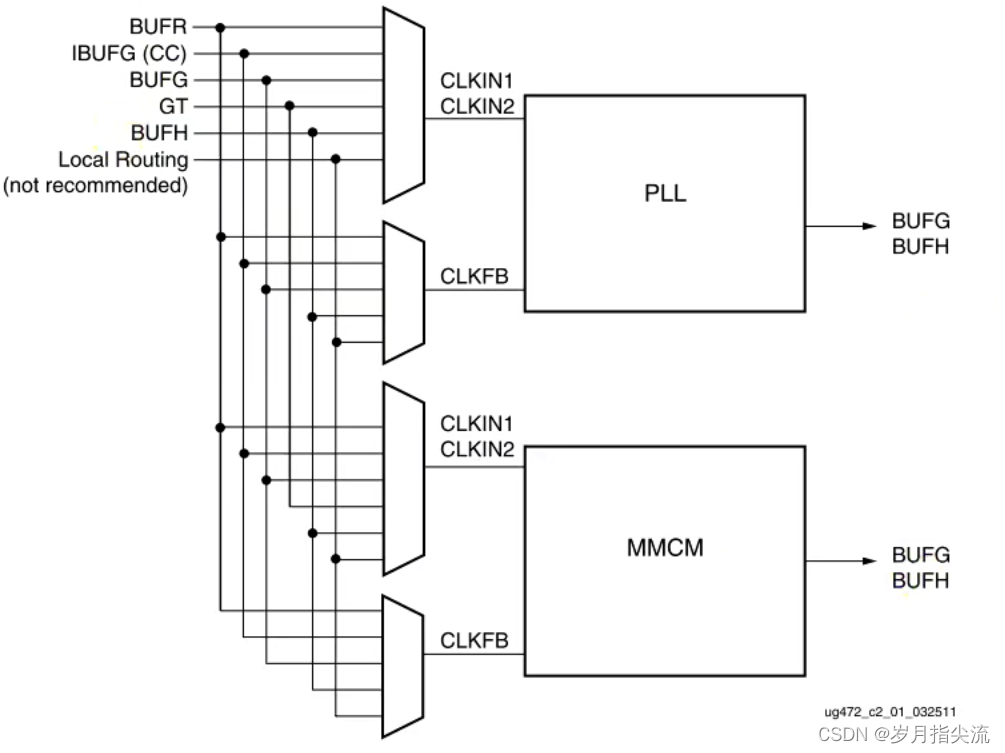

Xilinx7 系列器件中的时钟资源包含了CMT(全称 Clock Management Tile,即时钟管理单元),每个 CMT 由一个 MMCM(全称 Mixed-Mode Clock Manager,即混合模式时钟管理)和一个 PLL(全称 Phase Locked Loop,即锁相环)组成,

- MMCM(混合模式时钟管理):是基于 PLL 的新型混合模式时钟管理器,实现了最低的抖动和抖动滤波,为高性能的 FPGA 设计提供更高性能的时钟管理功能。

- MMCM 在 PLL 的基础上加上了相位动态调整功能,

- PLL:为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取数据 等。PLL 用于振荡器中的反馈技术。

- 锁相环拥有强大的性能,可以对输入到 FPGA 的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟;

MMCM 相对 PLL 的优势就是相位可以动态调整,但 PLL 占用的面积更小,而在大部分的设计当中大家使用 MMCM 或者 PLL 来对系统时钟进行分频、倍频和相位偏移都是完全可以的。

2、FPGA CMT 框图

下图为 7 系列 FPGA CMT 的一个简单的结构,最左边是输入的一些时钟源,最右边是输出。

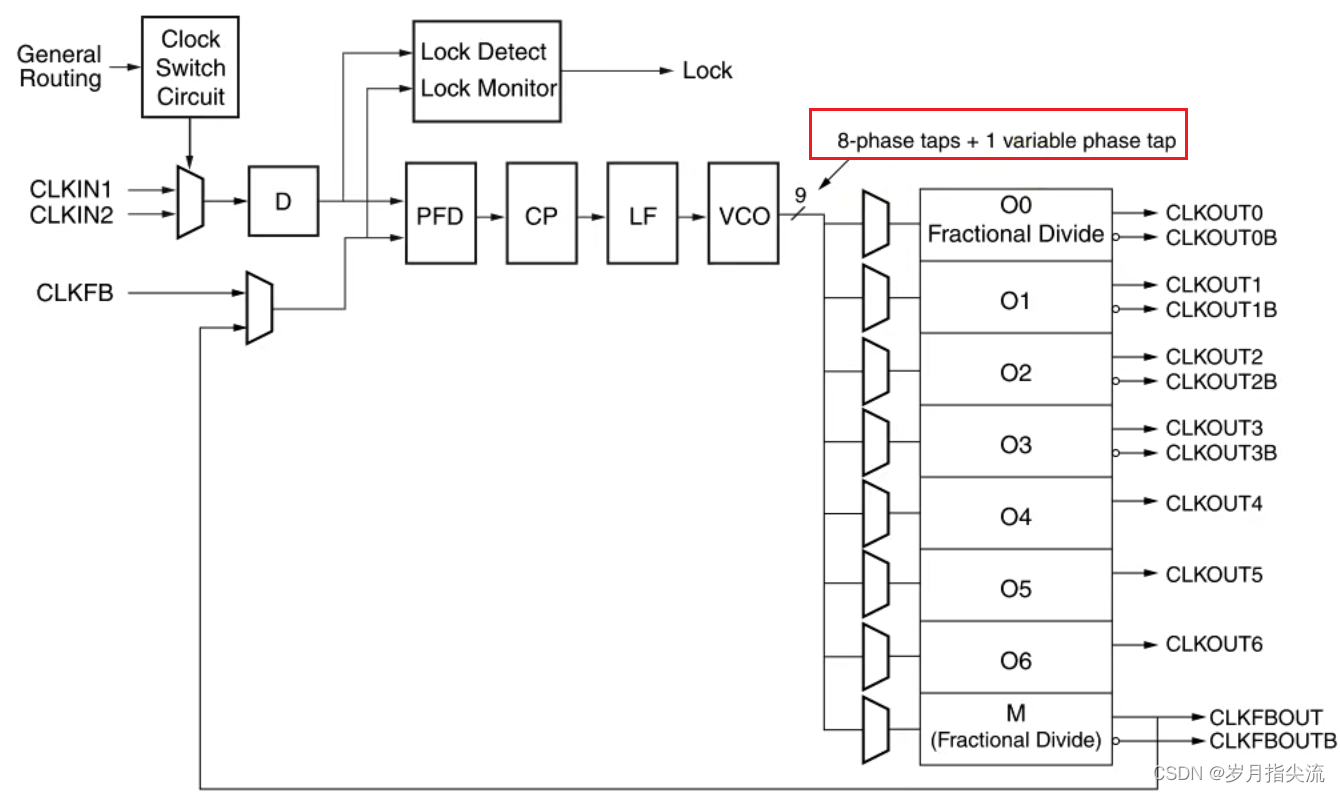

3、MMCM 框图

下图是 MMCM 的框图,可以看到它包含 8 个相位的拍 + 1 个可变相位拍

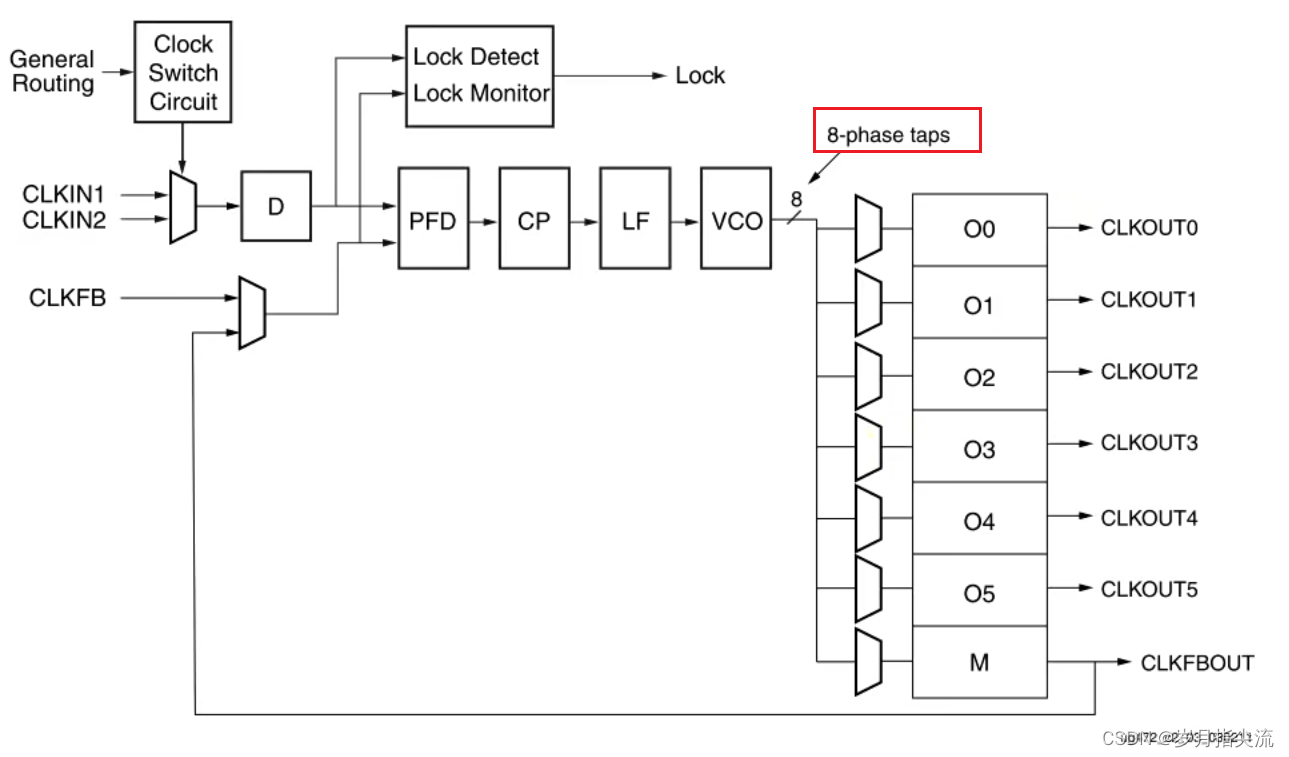

4、PLL 框图

下图是 PLL 的框图,可以看到它只包含 8 个相位的拍

二、创建工程

1、创建工程

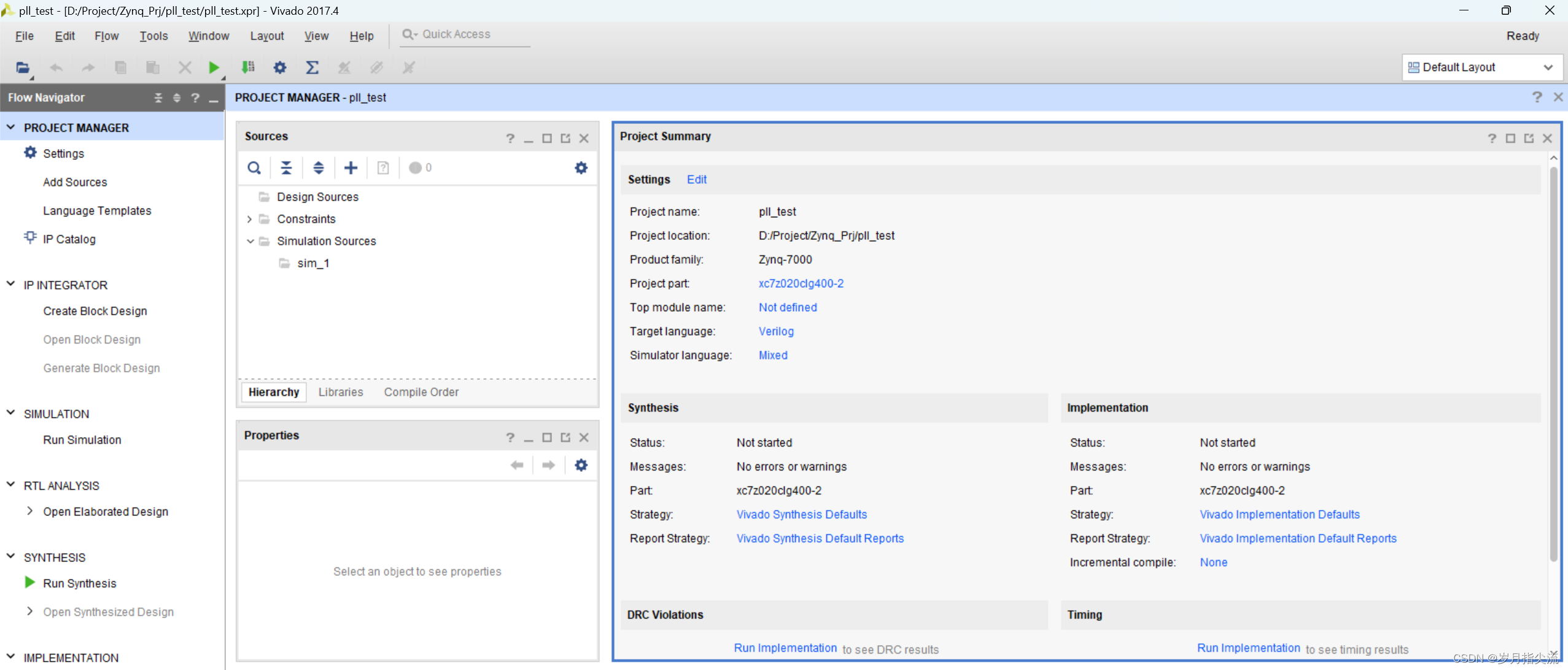

创建一个名字为 pll_test 的工程

2、PLL IP 核配置

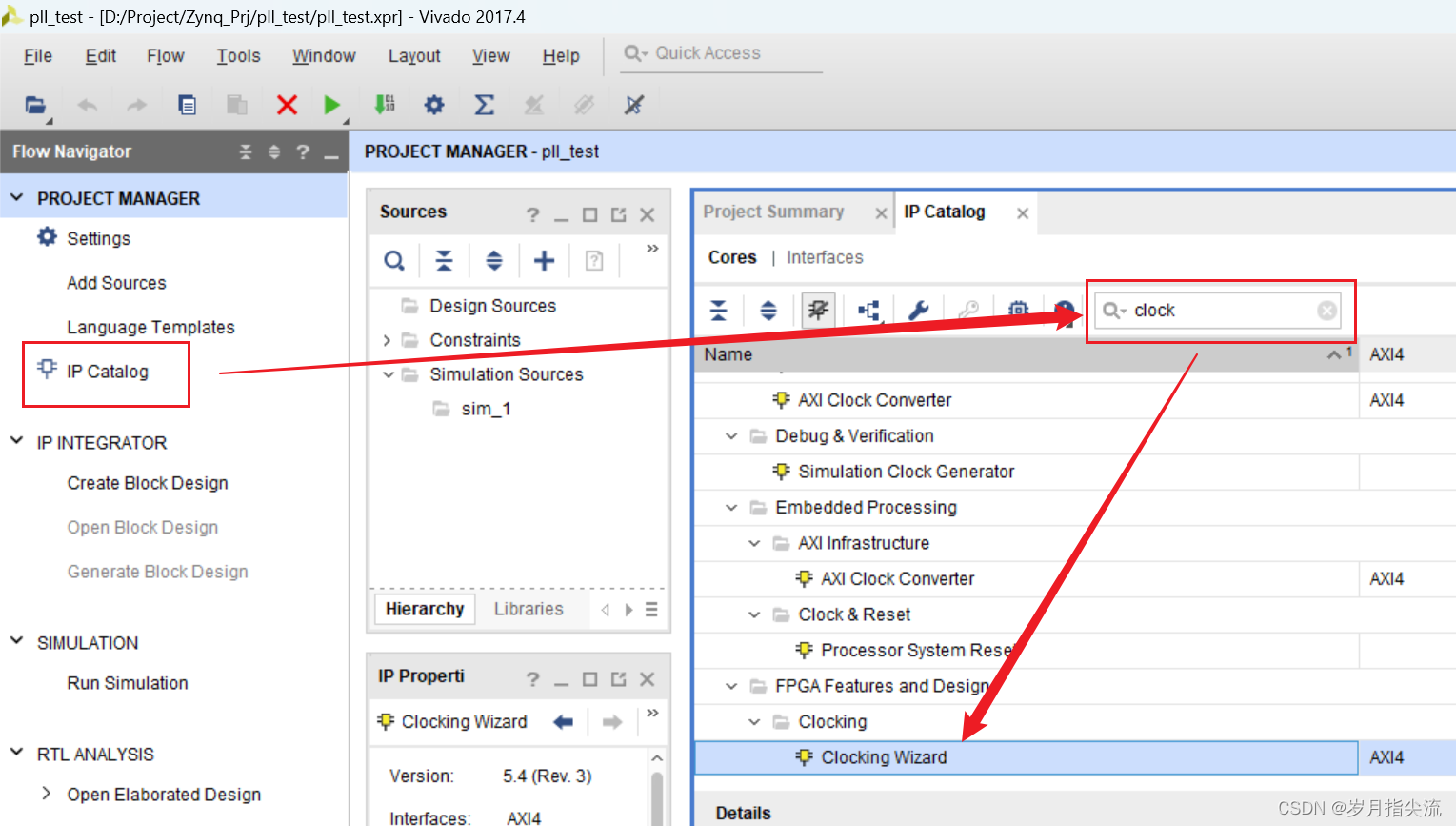

1、点击 IP Catalog,搜索 clock,找到 Clocking Wizard 并双击

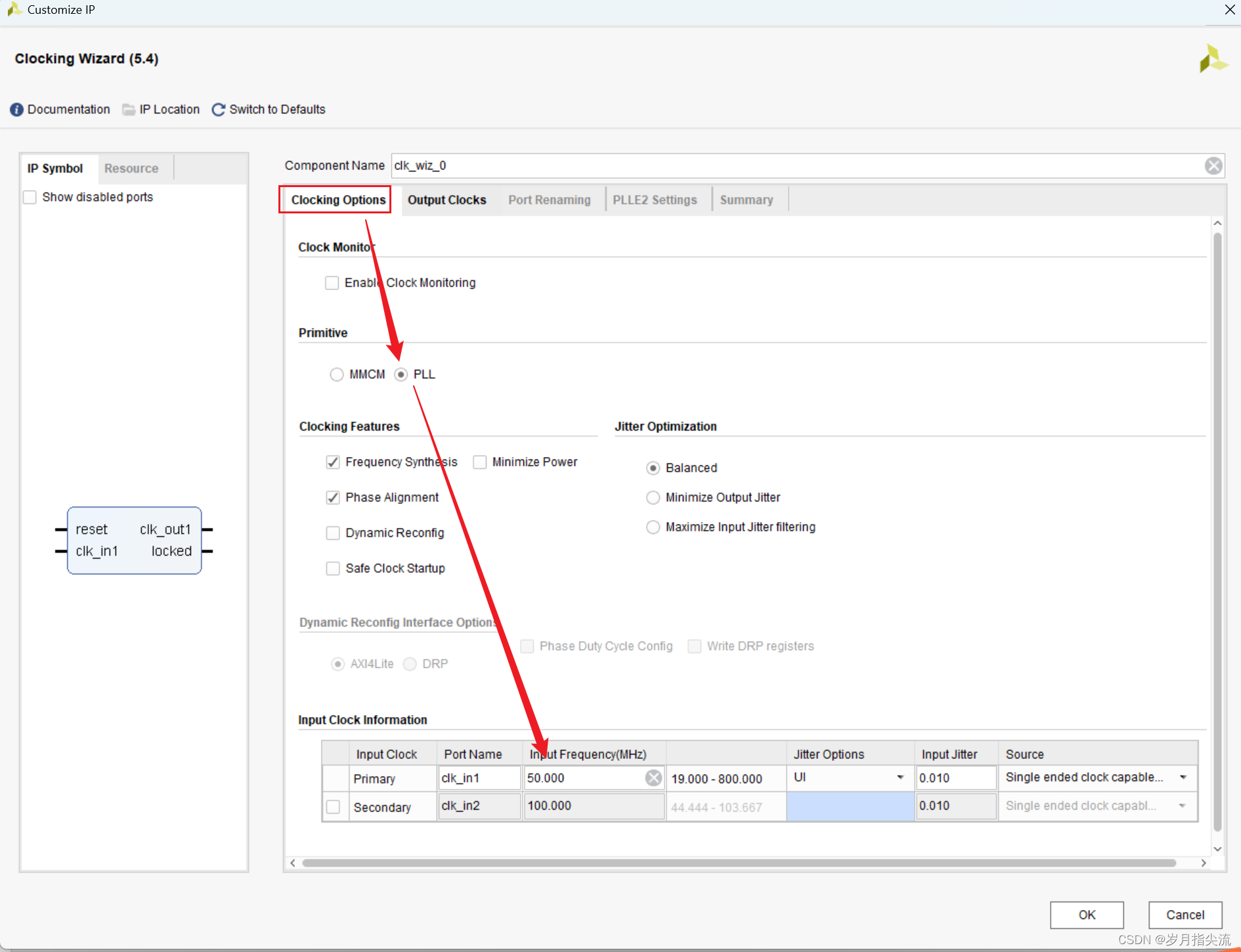

2、在 Clocking Option 下按如下图进行配置

- Primitive 选择 PLL

- Input Clock Information 中的主时钟的输入频率填上我们板子晶振频率:50MHz

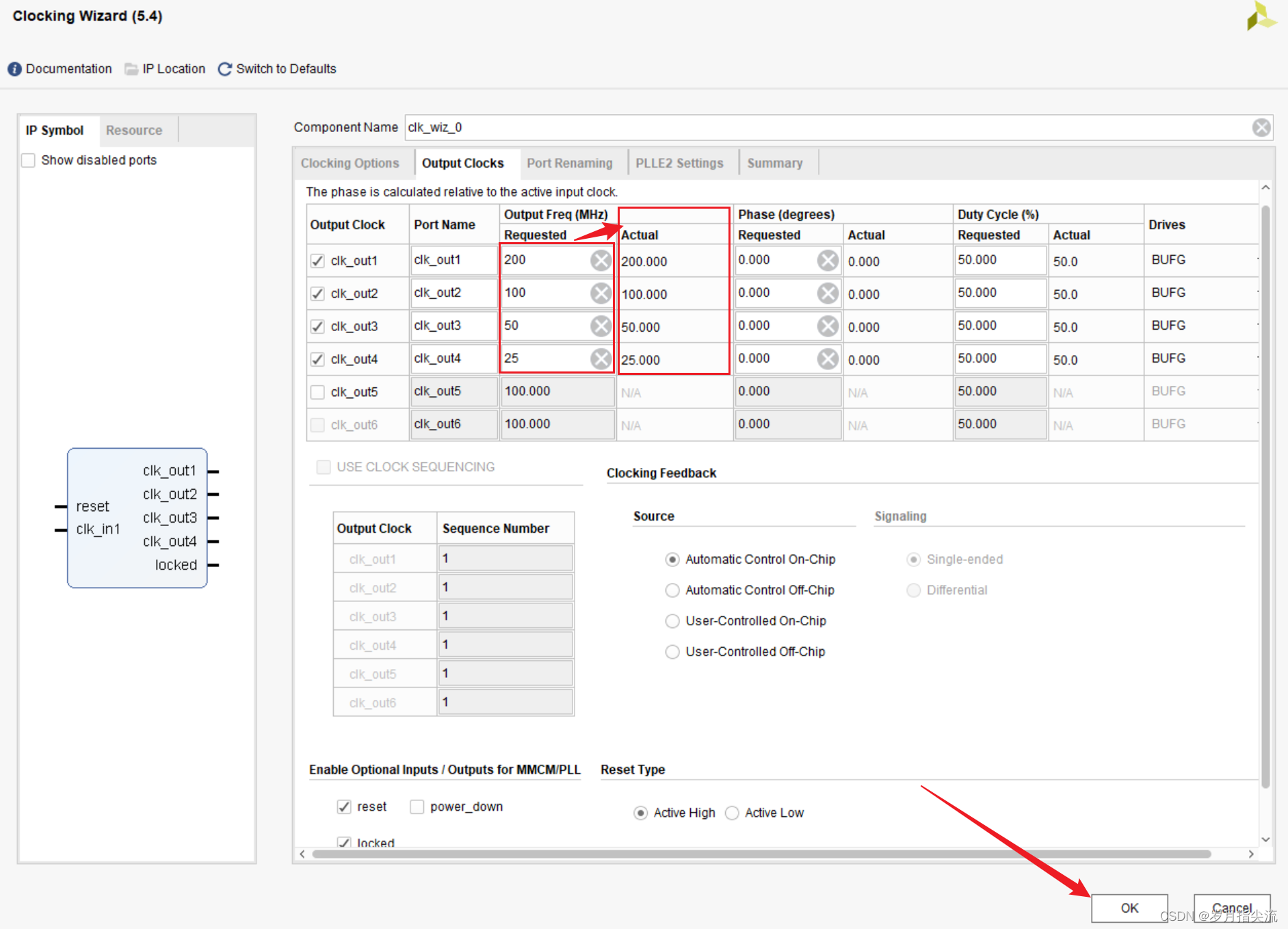

3、在 Output Clocks 下按如下图进行配置,并点击 OK

我们输出 200MHz、100MHz、50MHz、25MHz 这么四路不同频率的时钟

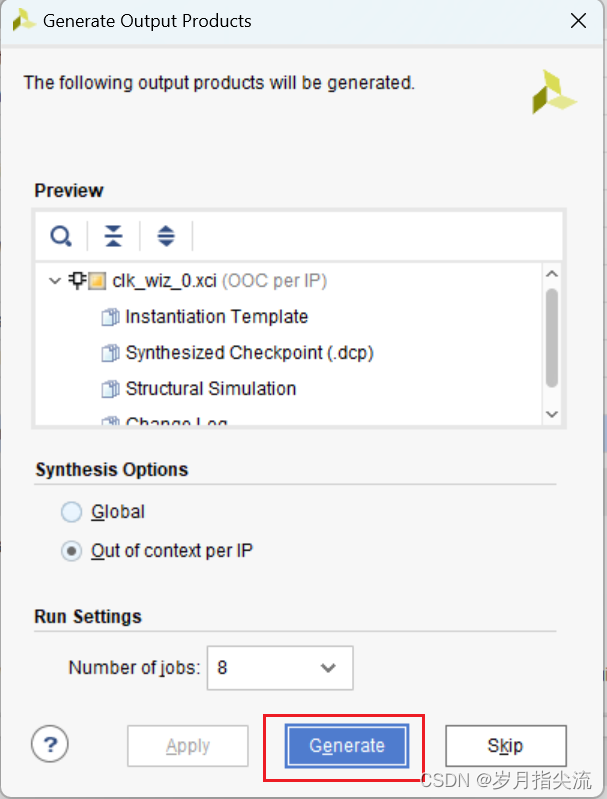

4、点击生成 Generate

3、进行例化

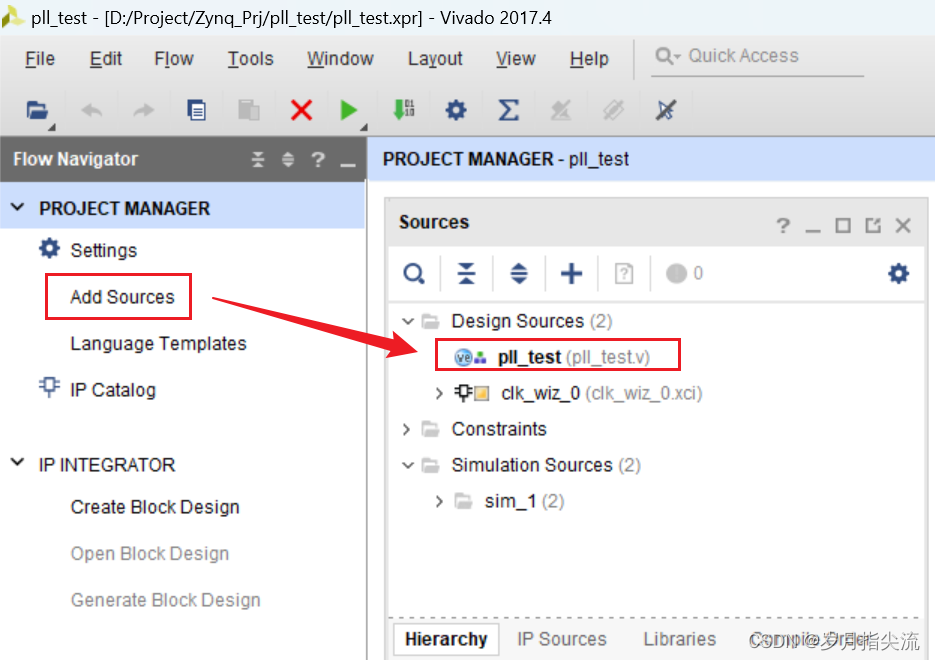

1、创建一个名为 pll_test.v 文件

2、复制例化模板到我们刚创建的 pll_test.v 文件中

3、对 pll_test.v 文件进行修改,修改之后的代码如下(这里我们只输出 25MHz 信号)

`timescale 1ns / 1psmodule pll_test(input sys_clk, // 50MHzinput rst_n,output clk_out);wire pll_locked; clk_wiz_0 clk_inst(// Clock out ports.clk_out1(), // output clk_out1.clk_out2(), // output clk_out2.clk_out3(), // output clk_out3.clk_out4(clk_out), // output clk_out4// Status and control signals.reset(~rst_n), // input reset.locked(pll_locked), // output locked// Clock in ports.clk_in1(sys_clk)); // input clk_in1 endmodule

三、进行仿真

1、创建仿真文件

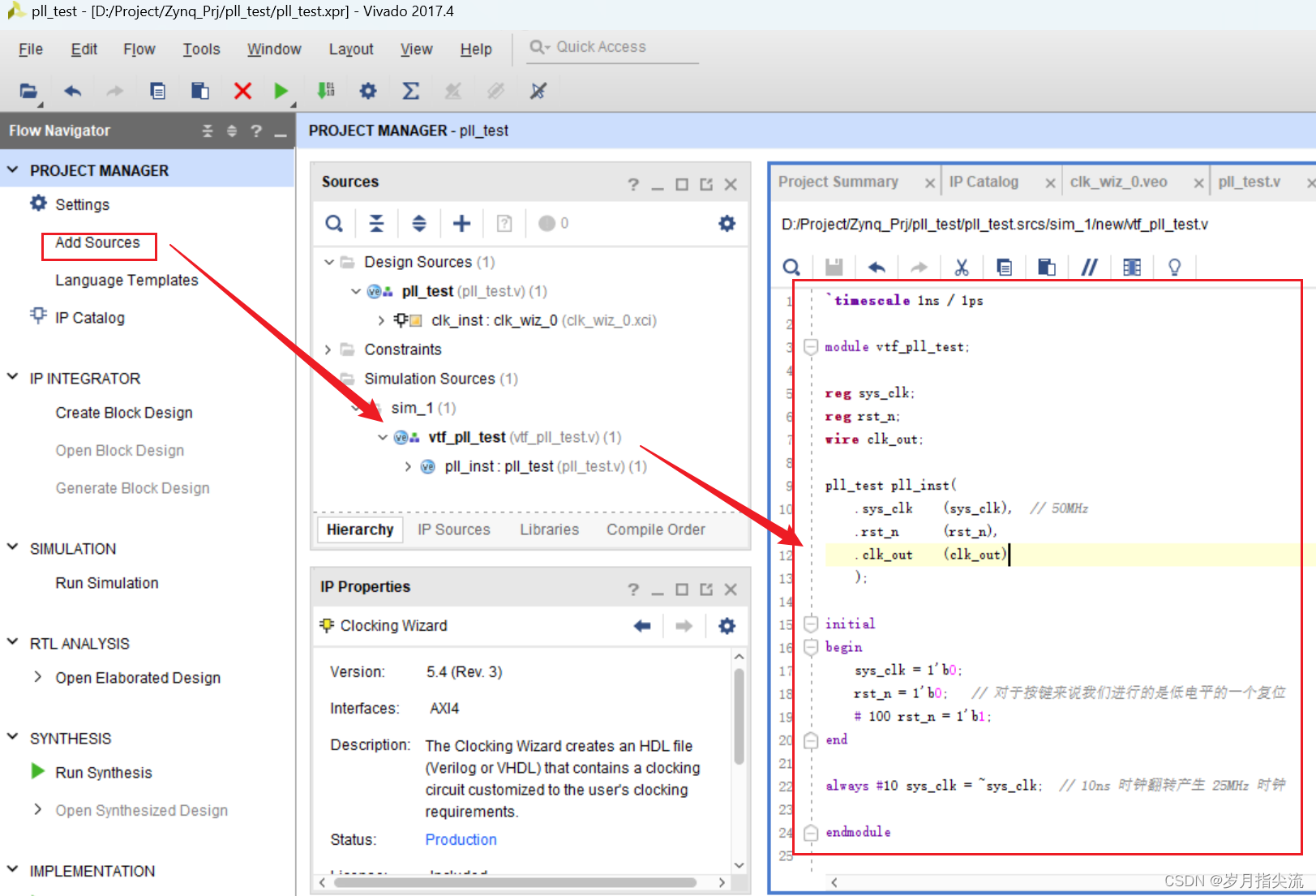

创建名为 vtf_pll_test.v 的仿真文件,并进行例化编写 verilog 仿真程序

`timescale 1ns / 1psmodule vtf_pll_test;reg sys_clk;

reg rst_n;

wire clk_out;pll_test pll_inst(.sys_clk (sys_clk), // 50MHz.rst_n (rst_n),.clk_out (clk_out));initial

beginsys_clk = 1'b0;rst_n = 1'b0; // 对于按键来说我们进行的是低电平的一个复位# 100 rst_n = 1'b1;

endalways #10 sys_clk = ~sys_clk; // 10ns 时钟翻转产生 25MHz 时钟endmodule

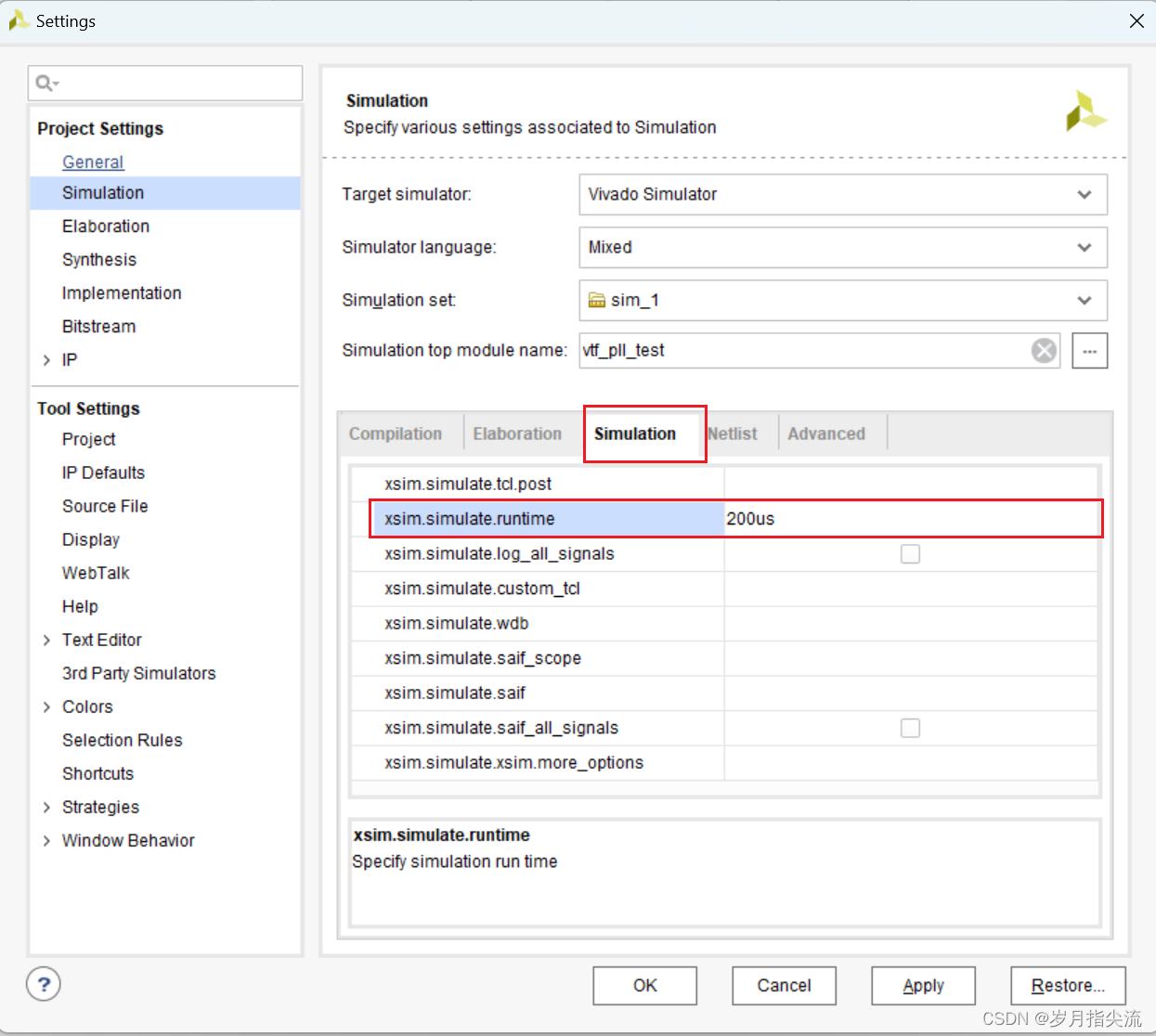

2、进行仿真设置

①、右键 Run Simulation -> Simulation Settings…

②、设置仿真时间,这里填 200us 即可

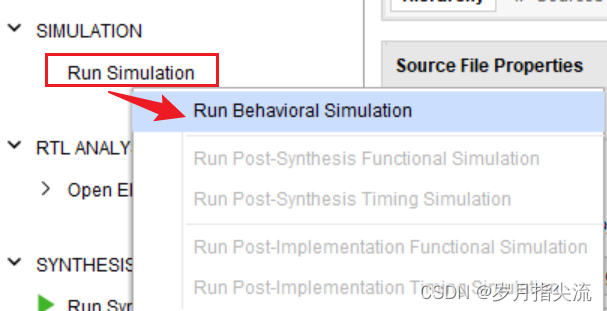

3、进行行为级仿真

①、左键 Run Simulation -> Run Behavioral Simulation

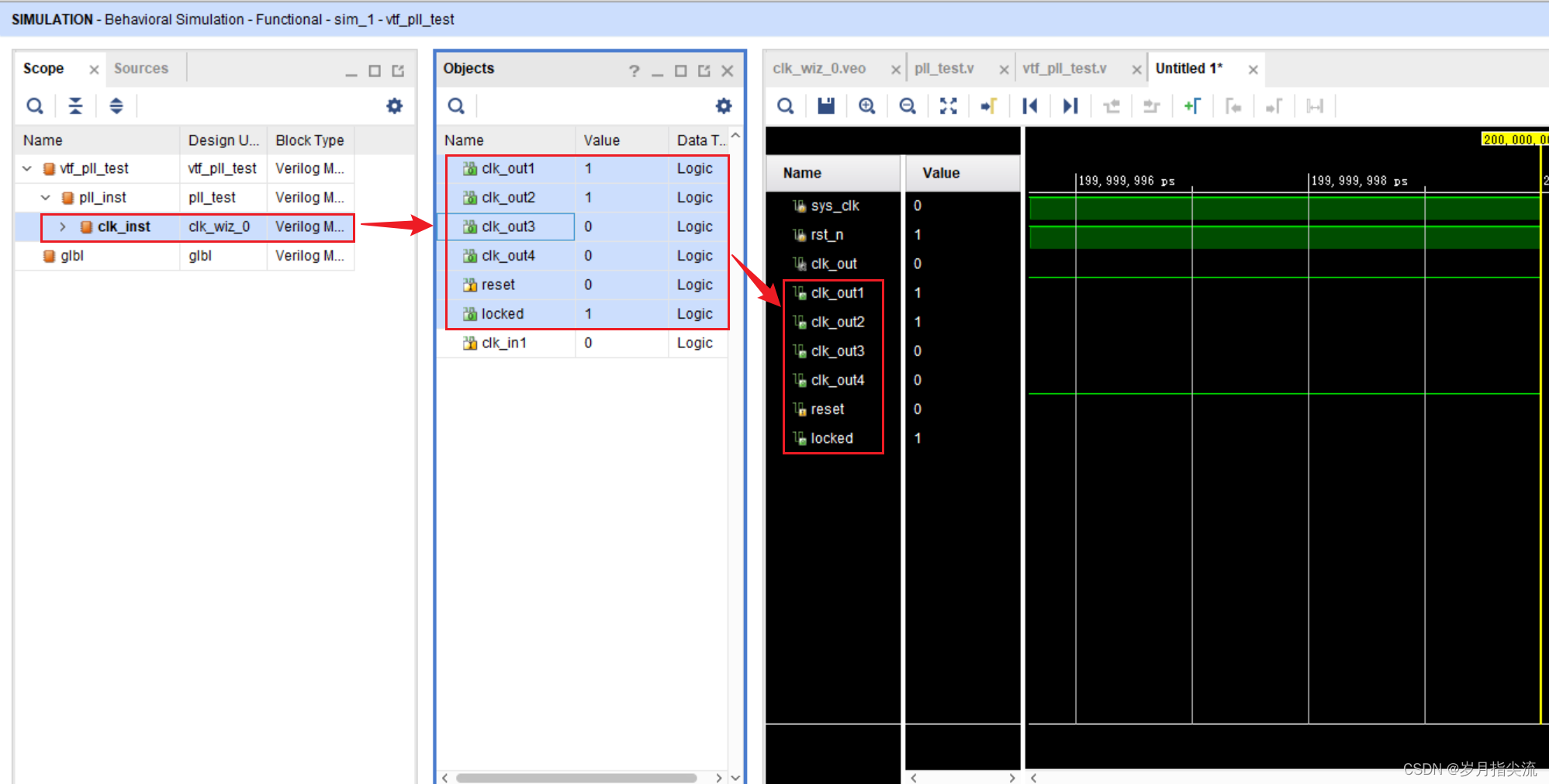

②、将 vtf_pll_test 下的 pll_inst 下的 clk_inst 的 clk_out1、clk_out2、clk_out3、clk_out_4、reset、locked 拖拽到仿真界面 Name 栏下

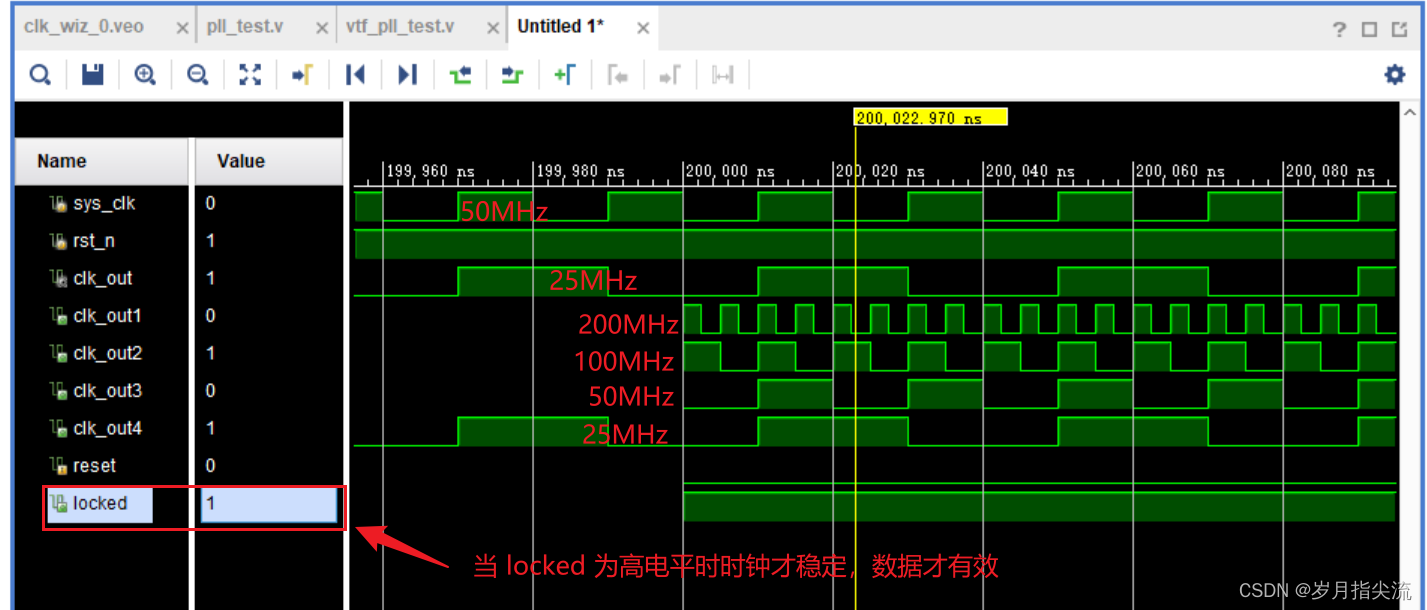

③、点击 Run for 10us,可以看下图结果

四、硬件验证

1、引脚绑定

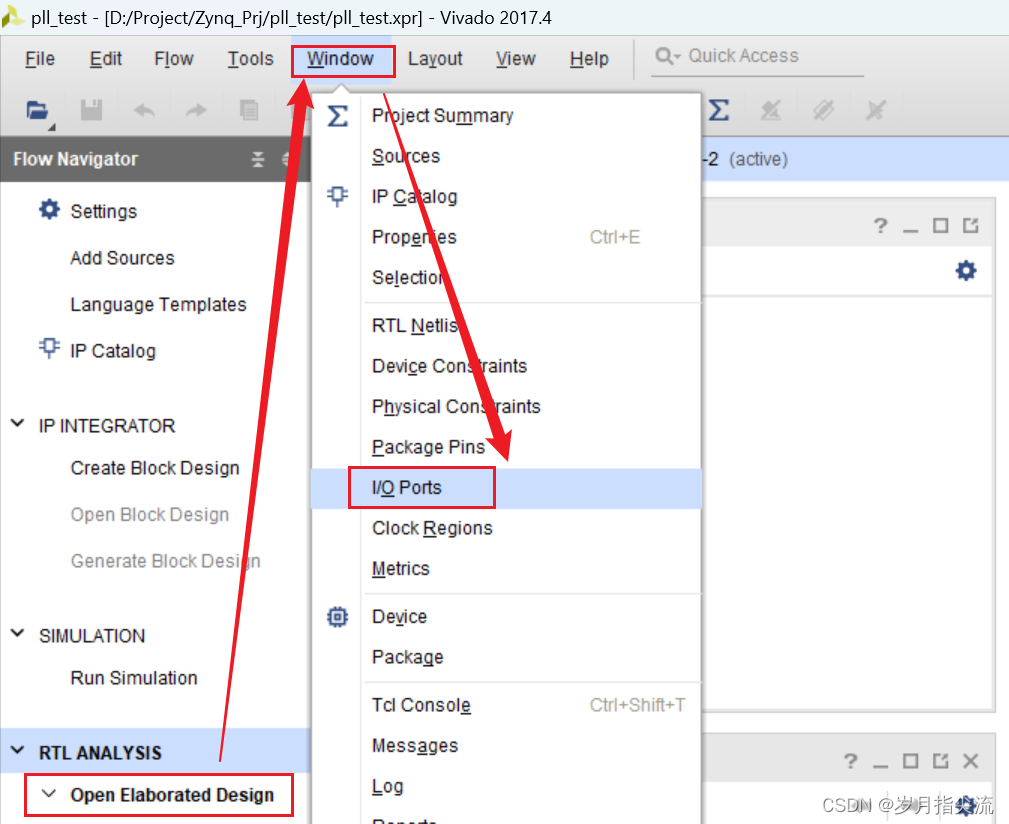

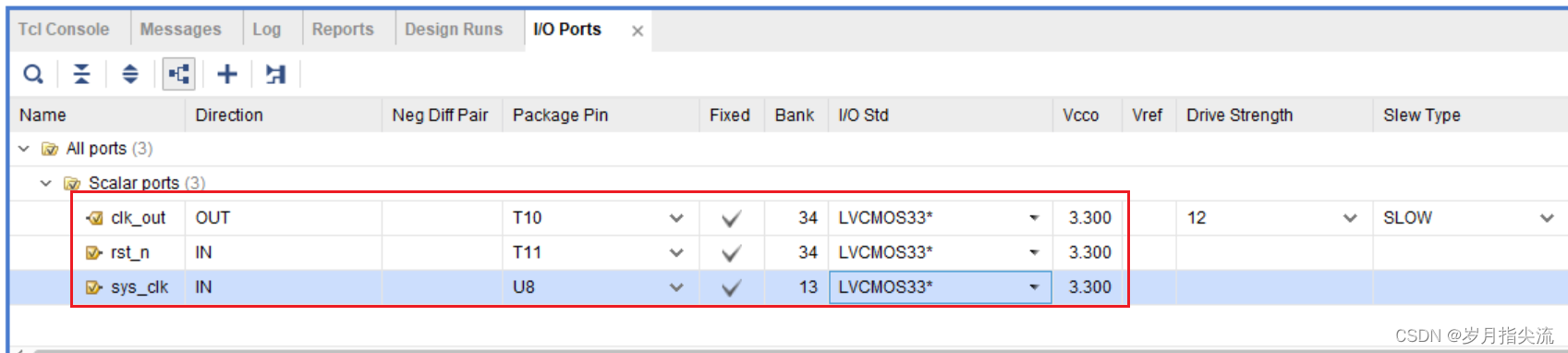

1、点击 “Open Elaborated Design”,再打开 Window 下的 I/O Ports

2、查看原理图

①、T11 -> rst_n,T0 -> clk_out

②、U18 -> sys_clk

③、因此分配情况如下:

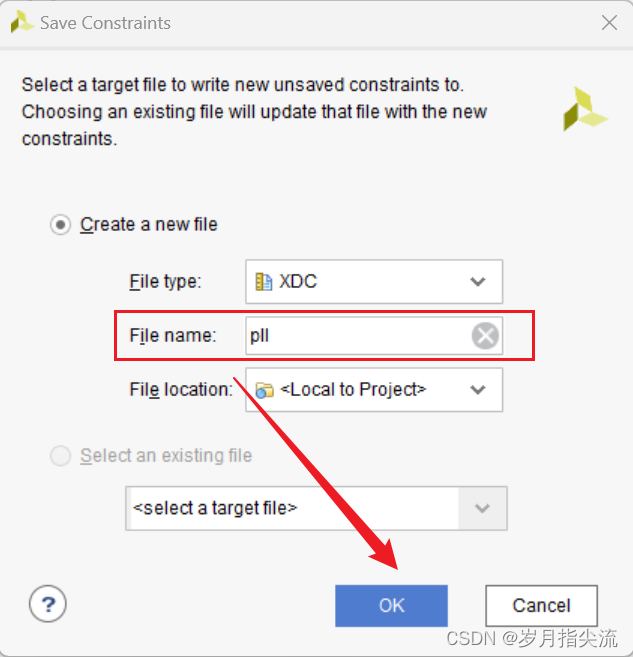

④、进行保存

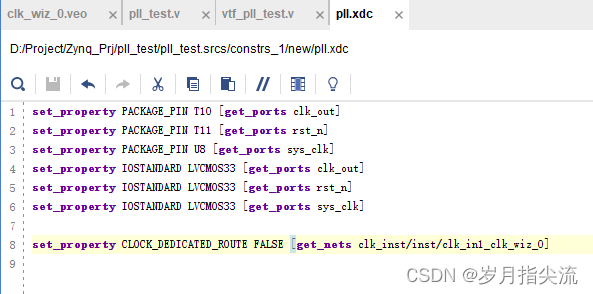

⑤、生成的 pll.xdc 文件如下图:

2、生成比特流文件

①、点击 “Generate Bitstream”,直接生成 bit 文件

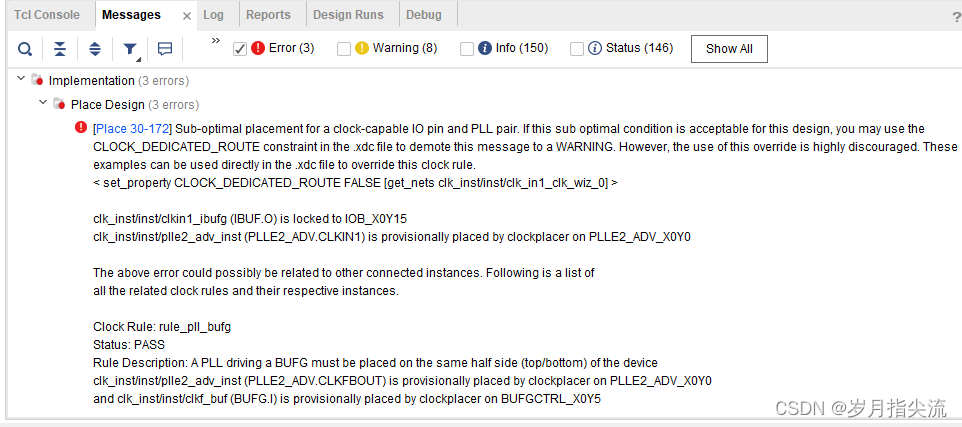

出现了如下报错:

[Place 30-172] Sub-optimal placement for a clock-capable IO pin and PLL pair. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_inst/inst/clk_in1_clk_wiz_0] >

clk_inst/inst/clkin1_ibufg (IBUF.O) is locked to IOB_X0Y15clk_inst/inst/plle2_adv_inst (PLLE2_ADV.CLKIN1) is provisionally placed by clockplacer on PLLE2_ADV_X0Y0The above error could possibly be related to other connected instances. Following is a list of

all the related clock rules and their respective instances.Clock Rule: rule_pll_bufg

Status: PASS

Rule Description: A PLL driving a BUFG must be placed on the same half side (top/bottom) of the deviceclk_inst/inst/plle2_adv_inst (PLLE2_ADV.CLKFBOUT) is provisionally placed by clockplacer on PLLE2_ADV_X0Y0and clk_inst/inst/clkf_buf (BUFG.I) is provisionally placed by clockplacer on BUFGCTRL_X0Y5

把这条提示加入 XDC 约束文件里面即可,原理就是绕过 PAR 的检查。

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_inst/inst/clk_in1_clk_wiz_0]

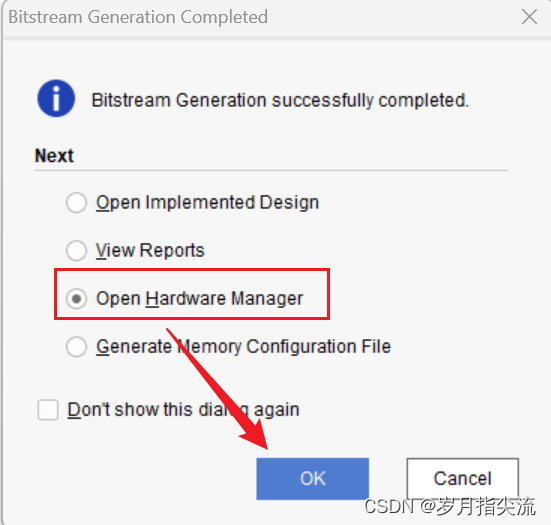

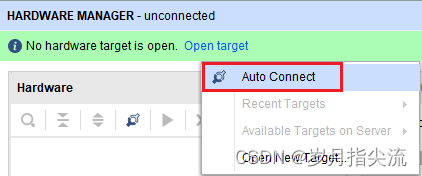

②、选择 Open Hardware Manager 并点击 OK

③、插上 fpga 仿真器及其电源,选择 Auto Connect

④、右键 xc7z020_1 -> Program Device

3、验证

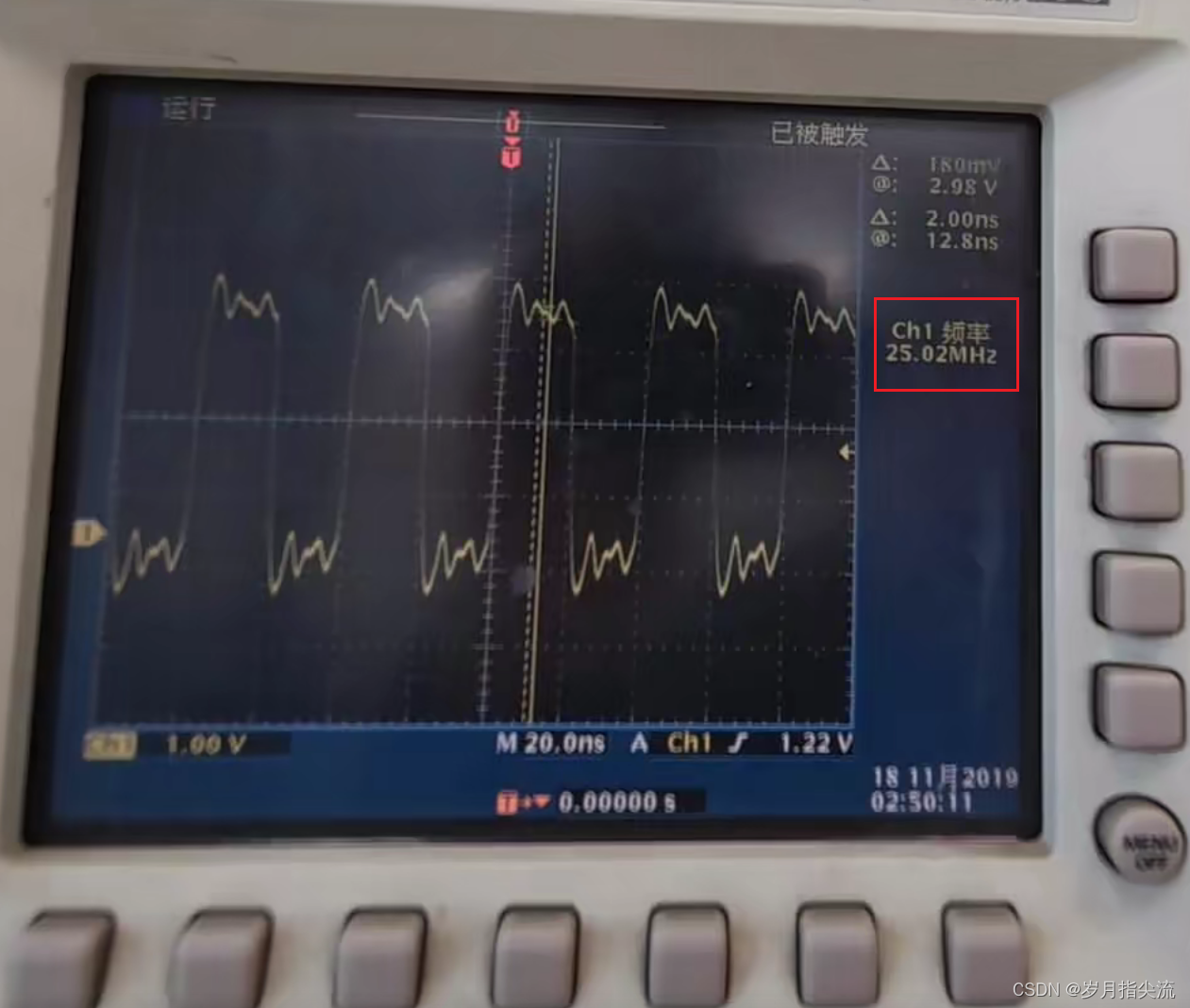

找一个示波器用探头接到 T10 引脚查看输出,可以看到 25MHz 方波信号

五、资源自取

基于vivado 2017.4 的 pll 测试

我的qq:2442391036,欢迎交流!