有关php动态网站建设的图片百度搜索热词查询

目录

1.1数据的表示

1.2数值表示范围

1.3浮点的运算

1.4计算机结构

1.5计算机体系结构分类——Flynn

1.6指令的基本概念

1.7寻址方式

1.8CISC与RISC

1.9流水线

1.10层次化存储结构

1.11Cache

1.12主存——编址与计算

1.13总线

1.14串联系统与并联系统

1.15N模混合系统

1.16校验码

欢迎读者阅读我的文章,这个系列主要是与软件设计师相关的知识点,将这些知识点进行了一个简单的归纳和总结,所以需要一定的计算机基础,可供刚开始学的朋友和复习的朋友进行梳理。创作不易,如果喜欢的话,点个赞支持一下吧!

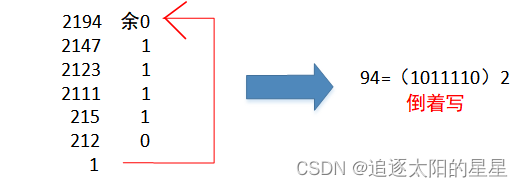

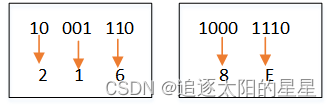

1.1数据的表示

(按权展开)

二进制:

七进制:

十进制转R进制(短除法)

二进制转八进制与十六进制

0x8E、(8E)16、8EH H代表16进制

| 码制 | 数值1 | 数值-1 | 1-1 |

| 0000 0001 | 1000 0001 | 1000 0010 | |

| 反码 | 0000 0001 | 1111 1110 | 1111 1111 |

| 补码 | 0000 0001 | 1111 1111 | 0000 0000 |

| 移码 | 1000 0001 | 0111 1111 | 1000 0000 |

1.2数值表示范围

| 码制 | 定点整数 | 定点小数 |

| 原码 | ||

| 反码 | ||

| 补码 | ||

| 移码 |

|

1.3浮点的运算

表示:N=尾数×基数^指数

过程:对阶>尾数计算>结果格式化

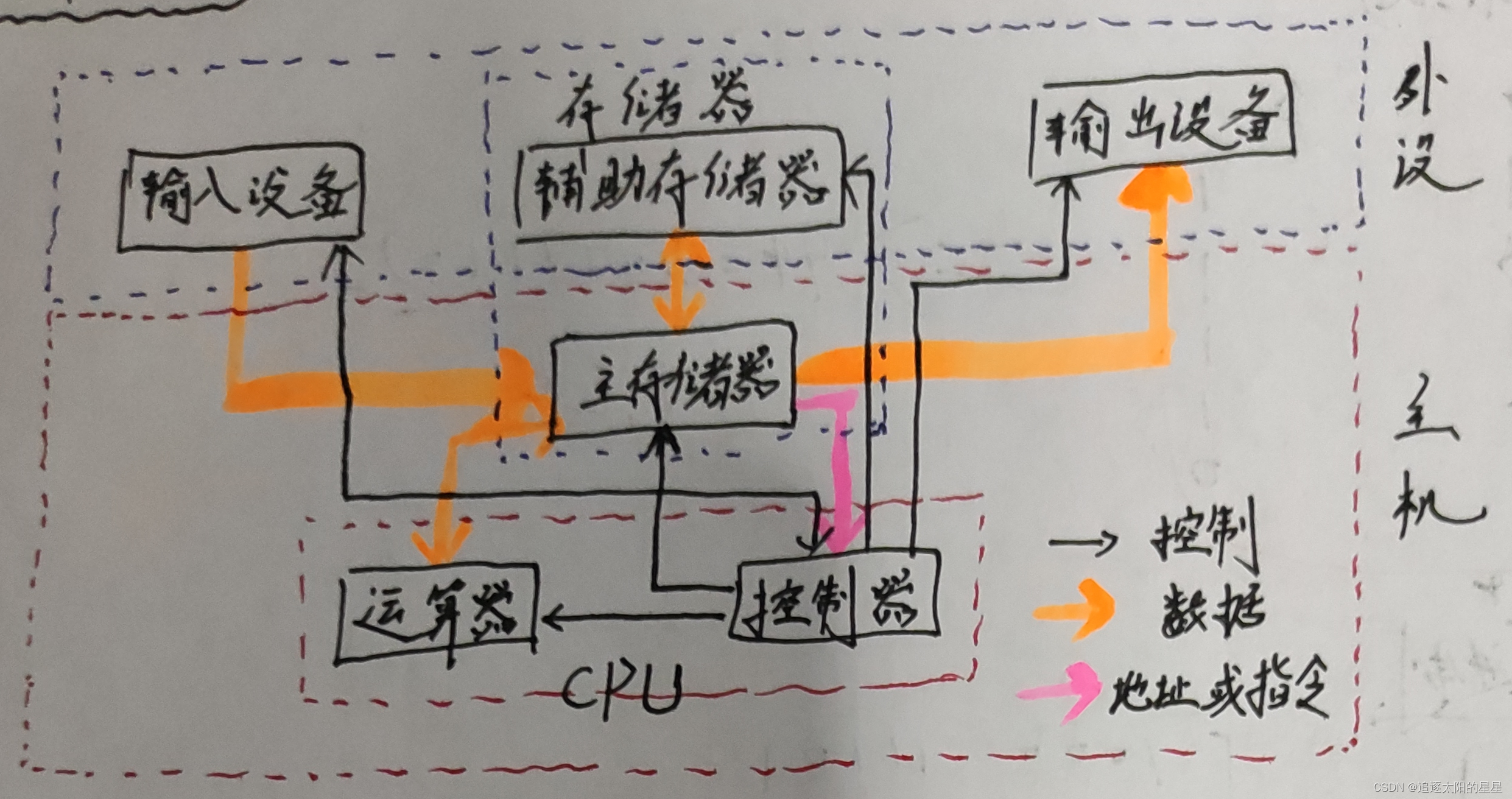

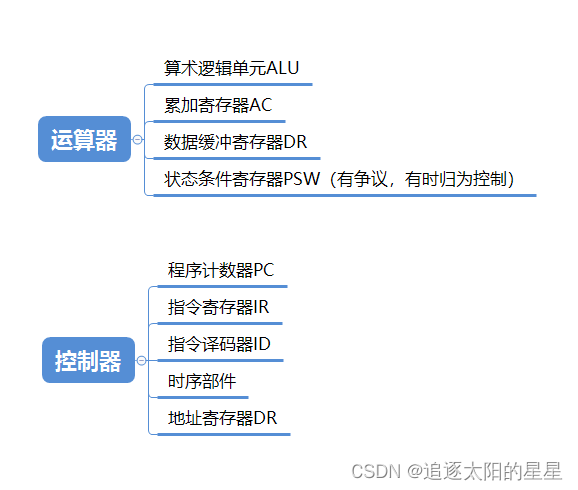

1.4计算机结构

1.5计算机体系结构分类——Flynn

| 体系结构类型 | 结构 | 关键特性 | 代表 |

| 单指令流丹数据流SISD | 控制部分:一个 处理器:一个 主存模板:一个 | 单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模板:多个 | 各处理器以异步方式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模板:多个 | 不可能,不切实际的 | 目前没有,文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模板:多个 | 能够实现作业、任务、指令等各级全面平行 | 多处理机系统多计算机 |

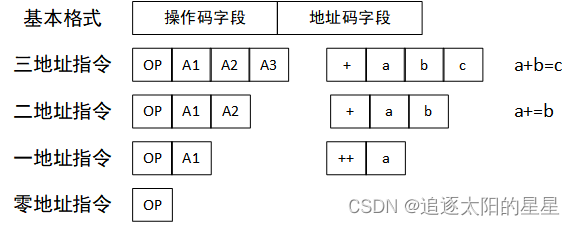

1.6指令的基本概念

1.7寻址方式

立即寻址方式

直接寻址方式

间接寻址方式

寄存器寻址方式

寄存器间接寻址方式

1.8CISC与RISC

| 指令系统类型 | 指令 | 寻址方式 | 实现方式 | 其它 |

| CISC(复杂) | 数量多,频率差别大,可变长格式 | 支持多种 | 微程序控制技术(微码) | 研制周期长 |

| RISC(精简) | 数量少,频率相近,定长格式,大部分为单周期指令,操作寄存器,只有Load/Store操作内存 | 支持方式少 | 增加了通用寄存器,硬布线逻辑控制为主,适合采用流水线 | 优化编译,有效支持高级语言 |

1.9流水线

流水线计算公式:一条指令执行时间+(指令条数-1)×流水线周期

(1)理论公式:(t1+t2+…+tk)+(n-1)×Δt

(2)实践公式:K×Δt+(n-1)×Δt

流水线吞吐率:TP=指令条数/流水线执行时间

流水线最大吞吐率:

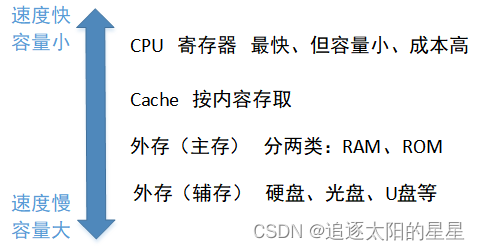

1.10层次化存储结构

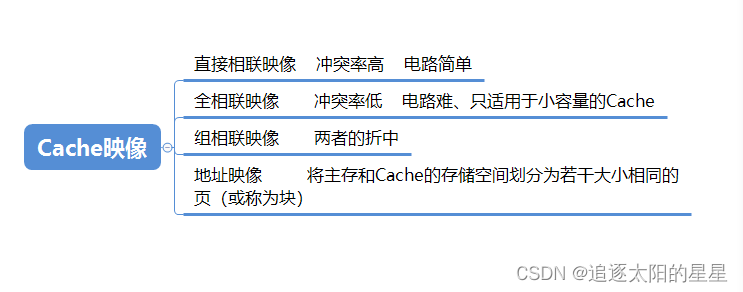

1.11Cache

t3:使用“Cache+主存储器”的系统的平均周期

h:Cache的访问命中率

t1:Cache的周期时间

t2:主存储器周期时间

1-h:又称为失效率(未命中率)

1.12主存——编址与计算

1Byte=8bit(位) 总片数=总容量/每片的容量

例如:

总容量:43FFH-4000H+1=4400H-4000H=400H

400H×16bit=2^10×16bit

每片的容量:(2^10×16bit)/4=256×16bit

1.13总线

一条总线同一时刻仅允许一个设备发送,但允许多个设备接收

数据总线 Data Bus

地址总线 Address Bus

控制总线 Control Bus

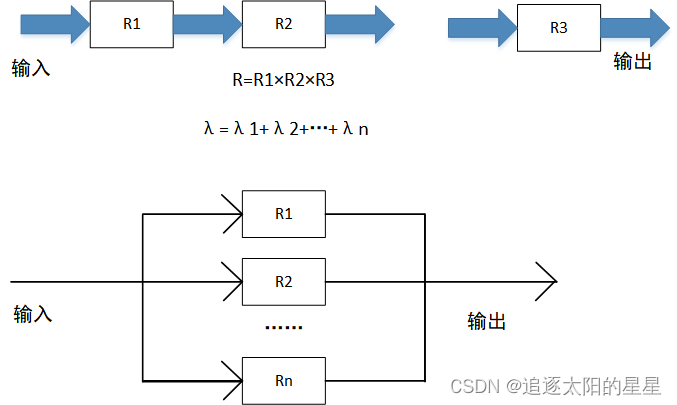

1.14串联系统与并联系统

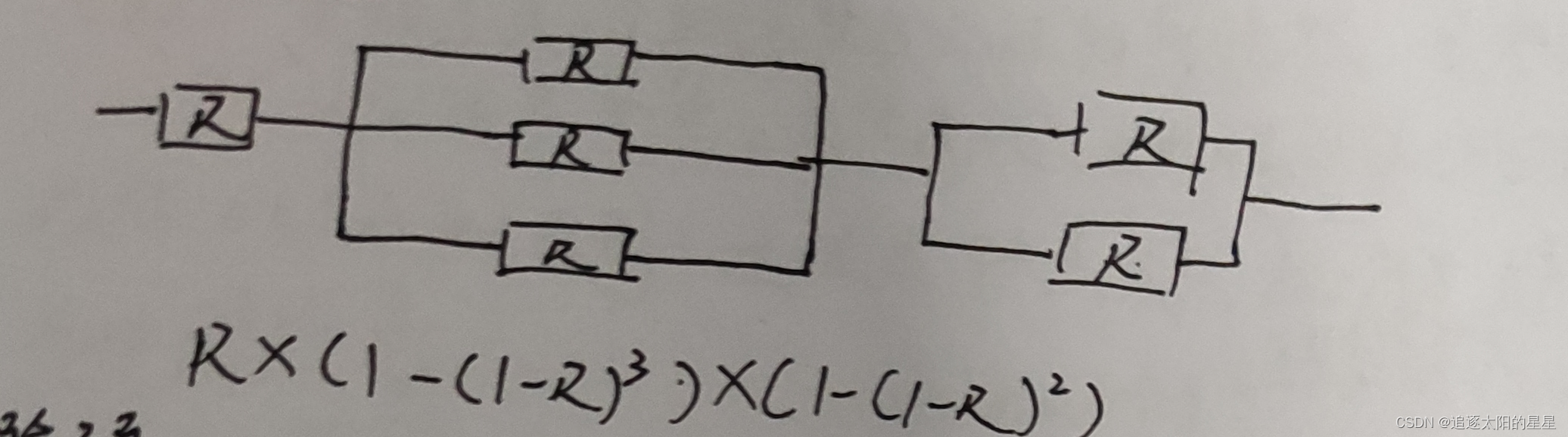

1.15N模混合系统

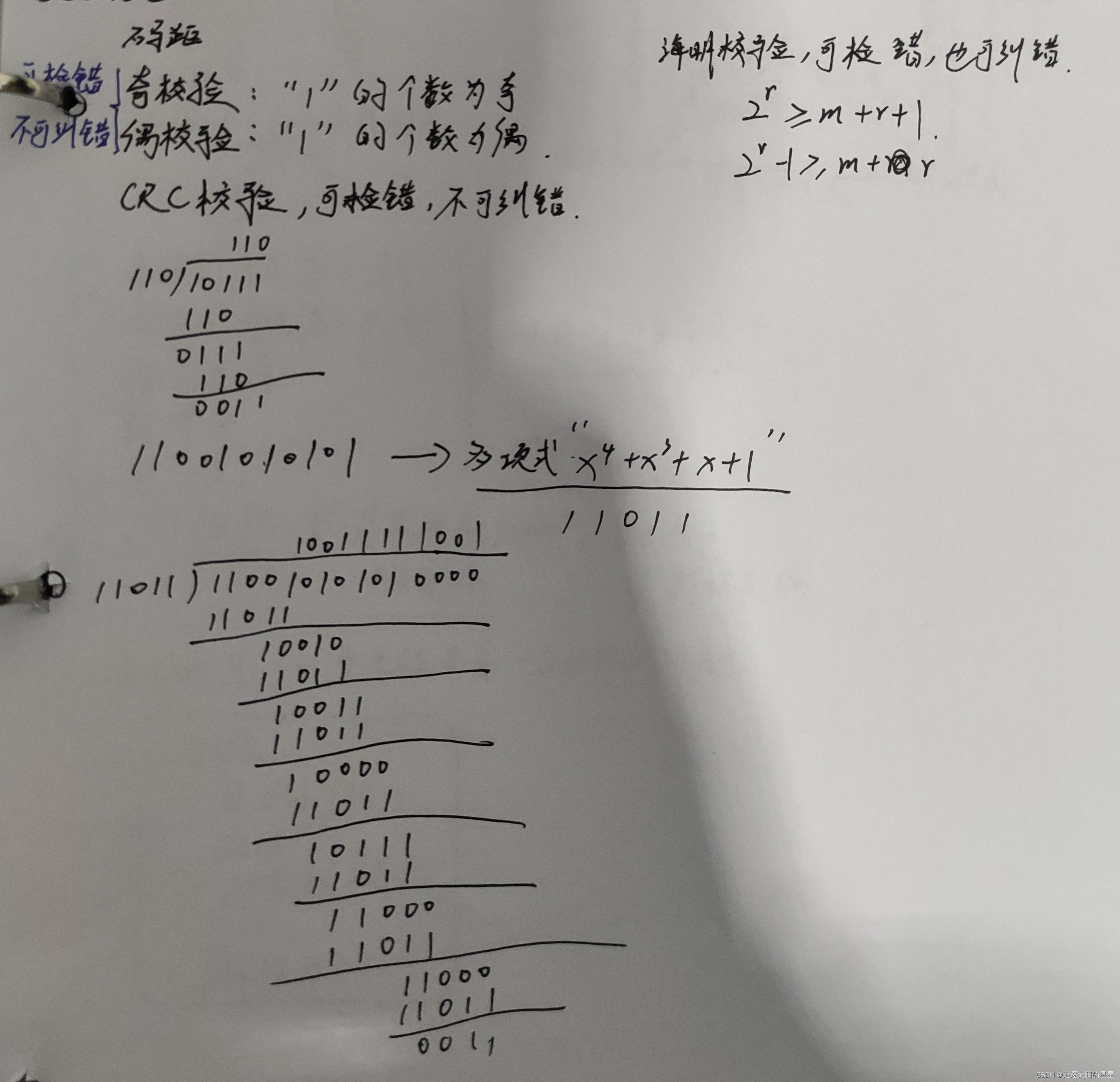

1.16校验码